PRODUCTION DATA - JUL 27, 2011

## Features

- K-Bus Interface useable as diagnostic interface to ISO 9141

- Data rate up to 9.600 Baud

- Very low standby current (30µA typical)

- Output slewrate control to reduce EMI

- Internal monitoring of prohibited conditions

- Supply voltage range VS 6.9V to 19V

- Supply voltage range VDD 4.5V to 5.5V

- Bus-line input voltage range 24V to + 30V

- 40°C to + 125°C operating temperature

- SO14n package

# Applications

Automotive bus systems

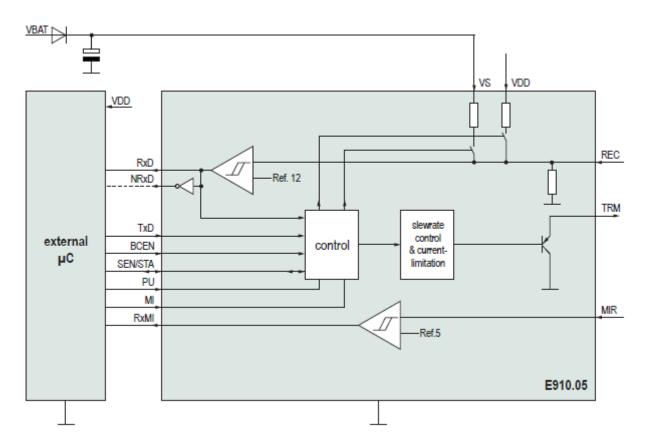

# **Brief Functional Description**

The IC is designed for communication via bidirectional serial data channels. In addition to the level conversion of transmit and receive signals from the microcontroller's voltage level to the 12V bus level, the device includes plausibility checks in order to guarantee undisturbed bus communication in case of corrupted data from the microcontroller. Undefined states are avoided during low voltage conditions by means of a Power-on-Reset which blocks the outputs. The inputs feature internal pull-up and pull-down current sources to maintain defined levels. The bus pins TRM and REC feature a wide input voltage range from – 24V up to +40V.

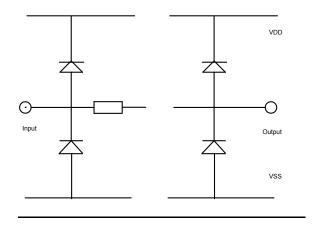

# **Typical Application**

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

ELMOS Semiconductor AG

QM-No.: 25DS0017E.00

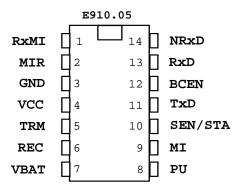

# 1. Package and Pinout

## 1.1. Package Pin Description

| Pin | Name    | Description                   |

|-----|---------|-------------------------------|

| 1   | RxMI    | Receive MI Bus, Output to MPU |

| 2   | MIR     | MI Bus receive                |

| 3   | GND     | Ground                        |

| 4   | VCC     | +5V Supply line               |

| 5   | TRM     | Transmit pin                  |

| 6   | REC     | Receive pin                   |

| 7   | VBAT    | +12V Battery supply           |

| 8   | PU      | Activate pull-up              |

| 9   | MI      | MI Bus enable                 |

| 10  | SEN/STA | Transmit path status          |

| 11  | TxD     | Transmit data, input from MPU |

| 12  | BCEN    | Enable Bit Compare Function   |

| 13  | RxD     | Receive data, output from MPU |

| 14  | NRxd    | Inverted receive data         |

## 1.2. Package Pin Out

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

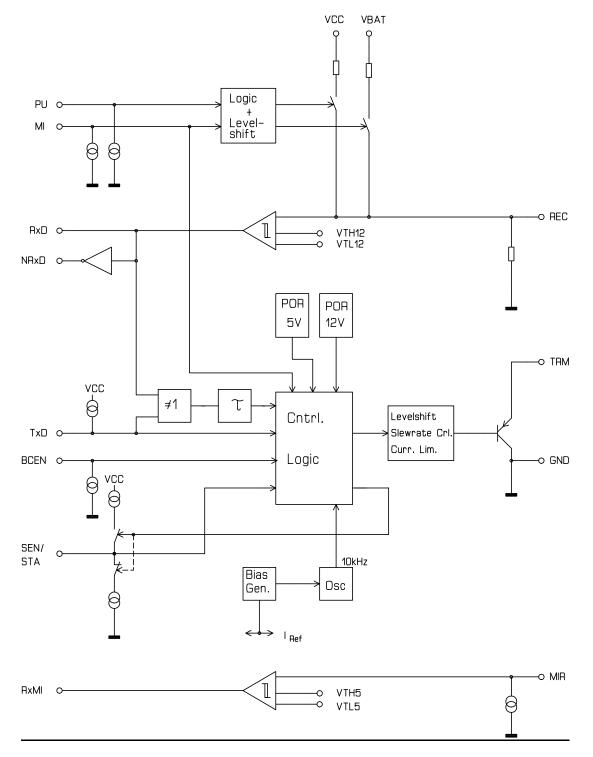

# 2. Block Diagram

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# 3. Operating Conditions

## 3.1. Absolute Maximum Ratings

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied.

Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages referred to ground (GND). Currents flowing into terminals are signed as positive, those drawn out of a terminal are negative.

| Parameter                      | Pin   | Symbol             | min     | max                   | Unit   |

|--------------------------------|-------|--------------------|---------|-----------------------|--------|

| Supply voltage                 | 4     | V <sub>CC</sub>    | - 0.3   | 6.5                   | V      |

| Supply current                 | 4     | ICC                |         | 10 0                  | mA     |

| Battery voltage<br>for T<500ms | 7     | VBAT               | - 0.3   | 30 0<br>40 0          | V<br>V |

| Supply current                 | 7     | IBAT               |         | 20 0                  | mA     |

| Input voltage                  | 8-12  | $V_{IN}$           | - 0.3   | V <sub>CC</sub> + 0.3 | V      |

| Input current                  | 8-12  | IIN                | - 10.0  | 10 0                  | mA     |

| Input voltage                  | 2     | VIN                | - 0.3   | V <sub>BAT</sub> +0.3 | V      |

| Input current                  | 2     | IIN                | - 10.0  | 10 0                  | mA     |

| Input voltage                  | 5,6   | VIN                | - 24.0  | 30 0                  | V      |

| for T<500ms                    |       |                    |         | 40 0                  | V      |

| Output current                 | 13,14 | IOUT               | - 10.0  | 10 0                  | mA     |

| Power dissipation TA = 85 °C   |       | Ртот               |         | 420 0                 | mW     |

| Thermal Resistance             |       | Rth <sub>J-A</sub> |         | 165 0                 | K/W    |

| (Junction to Ambient)          |       | 071                |         |                       |        |

| Junction Temperature           | TJ    |                    | + 150 0 | °C                    |        |

| Operating Range                | TOPT  | - 40.0             | + 125 0 | °C                    |        |

| Storage Temperature            |       | TSTG               | - 55.0  | + 150 0               | °C     |

PRODUCTION DATA - JUL 27, 2011

## **3.2. Recommended Operating Conditions**

The following conditions apply unless otherwise stated.

| Parameter                                        | Pin                    | Condition                                                                              | Symbol                             | min    | typ    | max                      | unit            |

|--------------------------------------------------|------------------------|----------------------------------------------------------------------------------------|------------------------------------|--------|--------|--------------------------|-----------------|

| Power On Res. Level V <sub>CC</sub>              | 4                      |                                                                                        | VCCPOR                             | 2.8    | 3.5    | 4.2                      | V               |

| Power On Res. Level VBAT                         | 7                      |                                                                                        | VBATPOR                            | 3.0    | 3.8    | 4.5                      | V               |

| Supply Current I <sub>CC</sub> +I <sub>BAT</sub> | 3                      | V <sub>CC</sub> = 5,0V, V <sub>BAT</sub><br>= 12,0V<br>Pins 1, 2, 5, 6, 814<br>open    | ICCBAT                             |        | 30.0   | 50.0                     | μA              |

| Pull down Current<br>PU, MI, BCEN                | 8, 9,<br>12            |                                                                                        | Ipd                                | 160.0  | 250.0  | 330.0                    | μA              |

| Pull up Current TxD                              | 11                     |                                                                                        | Ipu                                | -330.0 | -250.0 | -160.0                   | μA              |

| Pull down Current SEN/STA                        | 10                     |                                                                                        | IpdSen                             | 160    | 250    | 330.0                    | μA              |

| Pull up Current SEN/STA                          | 10                     |                                                                                        | IpuSen                             | -330.0 | -250.0 | -160.0                   | μA              |

| Input Low Level<br>PU,MI,BCEN,TxD,SEN/STA        | 8, 9,<br>10,<br>11, 12 |                                                                                        | ÝIL                                |        |        | 0.25                     | V <sub>CC</sub> |

| Input -High Level<br>PU,MI,BCEn,TxD,Sen/Sta      | 8, 9,<br>10,<br>11, 12 |                                                                                        | VIH                                | 0.75   |        |                          | V <sub>CC</sub> |

| Pull down Current MIR                            | 2                      |                                                                                        | I <sub>pd</sub>                    | 27.0   | 43.0   | 60.0                     | μA              |

| Input Low Level MIR                              | 2                      |                                                                                        | ν <sub>π</sub>                     |        |        | 1.4                      | V               |

| Input High Level MIR                             | 2                      |                                                                                        | VIH                                | 2.5    |        |                          | V               |

| Input Low Level REC                              | 6                      |                                                                                        | VIL                                |        |        | 0.4                      | VBAT            |

| Input High Level REC                             | 6                      |                                                                                        | VIH                                | 0.6    |        |                          | VBAT            |

| Hysteresis,                                      | 6                      |                                                                                        | V <sub>Hys</sub>                   |        | 50.0   |                          | mV              |

| Input Resistance REC<br>without Pull up          | 6                      | Tamb < 85°c                                                                            | R <sub>IN</sub><br>R <sub>IN</sub> | 330.0  | 800.0  | 1500.<br>0<br>1300.<br>0 | kΩ<br>kΩ        |

| 5 Volt Pull up Resistance<br>REC                 | 6                      | V <sub>CC</sub> = 5V, V <sub>out</sub> Pin<br>6 = 0V                                   | R <sub>pu5</sub>                   | 1.4    | 2.2    | 3.0                      | kΩ              |

| 12 Volt Pull up Resistance<br>REC                | 6                      | V <sub>BAT</sub> = 12V V <sub>out</sub><br>Pin 6 = 0V                                  | R <sub>pu12</sub>                  | 1.4    | 2.2    | 3.0                      | kΩ              |

| Maximum Active<br>Output Voltage REC             | 6                      | V <sub>BAT</sub> = 30V                                                                 | V <sub>0 max</sub>                 | 18.0   | 24.0   |                          | V               |

| Output Voltage TRM<br>under load                 | 5                      | $V_{CC} = 5,0V, V_{BAT}$<br>= 12,0V<br>Pin 10 = 0V<br>A) Pin 5: Load<br>Current = 40mA | V <sub>out</sub>                   |        | 1.1    | 1.4                      | v               |

|                                                  |                        | B) Pin 5: Load<br>Current = 10mA                                                       | V <sub>out</sub>                   |        | 0.8    | 1.0                      | v               |

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

PRODUCTION DATA - JUL 27, 2011

| Parameter                                  | Pin   | Condition                                            | Symbol           | min          | typ          | max   | unit     |

|--------------------------------------------|-------|------------------------------------------------------|------------------|--------------|--------------|-------|----------|

| Output Sink Current TRM<br>(Current Limit) | 5     | V <sub>OUT</sub> > Vfb                               | l <sub>lim</sub> | 30.0         | 70.0         | 140.0 | mA       |

| Output Sink Current TRM (before Fold Back) | 5     |                                                      | lout             |              |              | 180.0 | mA       |

| Fold Back Onset Voltage                    | 5     |                                                      | V <sub>fb</sub>  |              |              | 3.5   | V        |

| Input Resistance TRM                       | 5     | V <sub>out</sub> = -23 V<br>V <sub>out</sub> = -12 V | R <sub>in</sub>  | 15.0<br>40.0 | 40.0<br>80.0 |       | kΩ<br>kΩ |

| Output Leakage TRM                         | 5     | V <sub>OUT</sub> = 16V                               | ILeak            |              |              | 5.0   | μA       |

| Output Voltage<br>RxD, RxMI                | 1, 13 | I <sub>O</sub> = 1mA                                 | V <sub>OL</sub>  |              |              | 0.2   | VCC      |

| Output Voltage<br>RxD, RxMI                | 1, 13 | I <sub>O</sub> = -1mA                                | VOH              | 0.8          |              |       | VCC      |

| Output Voltage NRxD                        | 14    | I <sub>O</sub> = 1mA                                 | VOL              |              |              | 0.2   | VCC      |

| Output Voltage NRxD                        | 14    | I <sub>O</sub> = -1mA                                | VOH              | 0.8          |              |       | VCC      |

#### 3.1.2 A.C. Characteristics

| Parameter                            | Pin          | Condition                               | Symbol                                                      | min               | typ               | max               | unit           |

|--------------------------------------|--------------|-----------------------------------------|-------------------------------------------------------------|-------------------|-------------------|-------------------|----------------|

| Slew Rate Control TRM<br>in KIP Mode | 5            |                                         | dV/dT fall<br>dV/dT rise                                    | -2.5<br>1.0       | -1.5<br>1.5       | -1.0<br>2.5       | V/µs           |

| Debounce Time REC                    | 6, 13        | T > 85°C<br>high impulse<br>low impulse | <sup>t</sup> debh<br><sup>t</sup> debh<br><sup>t</sup> debl | 1.5<br>1.5<br>2.5 | 2.8<br>2.8<br>4.8 | 5.5<br>5.0<br>7.0 | μs<br>μs<br>μs |

| Delay Time<br>TxD->RxD/NRxD          | 11, 13       | KIP Mode                                | tdel                                                        |                   |                   | 20.0              | μs             |

| Delay Time<br>TxD->RxMI              | 1, 11        | MI-Mode                                 | <sup>t</sup> del                                            | 0.5               |                   | 4.0               | μs             |

| Bit Compare Time                     | 6, 10,<br>11 |                                         | t <sub>bc</sub>                                             | 35.0              | 40.0              | 70.0              | μs             |

| Recovery Time                        | 5, 6,<br>11  |                                         | t <sub>recov</sub>                                          | 30.0              | 50.0              | 75.0              | μs             |

| Delay Time for<br>Transmit Branch    | 5, 6,<br>11  |                                         | <sup>t</sup> sperr                                          | 0.920             | 1.36              | 1.8               | ms             |

| Permanent Low<br>switch-off Time     | 5, 6,<br>11  |                                         | t <sub>low</sub>                                            | 3.0               | 6.0               | 12.0              | ms             |

| Oscillator Frequency                 | 10           |                                         | fosc                                                        | 8.0               | 12.0              | 15.0              | kHz            |

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products. ELMOS Semiconductor AG Data Sheet 6/ 12 QM-No.: 2

PRODUCTION DATA - JUL 27, 2011

# 4. Functional Description

#### 4.1. General

The 910.05 Bus Interface is designed for the control of serial data channels. In addition to the level translation of Transmit and Receive signals from the processor voltage levels to the 12V bus levels, the device includes watchdog functions to ensure continued bus communication in the event of a failure of an individual bus member.

Undefined states are avoided during low voltage conditions by means of a Power-on-Reset which connects and disconnects the outputs and inputs. The inputs make use of internal Pull-up and Pull-down-resistors to maintain defined levels.

The bus control pins TRM and REC can operate or maintain a high impedance state from voltages between -24V and 40V independent of  $V_{BAT}$  and  $V_{CC}$ . This ensures that an open circuit ground connection or power supply interruption does not inhibit the operation of other devices using the bus.

### 4.2. Transmitter Path

When the Transmitter path is free, a Low level on the TxD pin switches the open-collector transistor on the TRM Pin on. In order to minimise the EMC radiation on the bus the rise and fall time of the transmit pulse on the TRM pin is conditioned by a slew rate controller. (MI = "0").

### 4.3. Receiver Path

The signal on the REC pin is permanently available at RxD and inverted on the NRxD pin. Transients are filtered by an internal debounce circuit on the comparator input.

The PU and MI pins can be programmed by the connection of a pull-up resistor to the  $V_{CC}$  or  $V_{BAT}$  supply (See Table)

For MI bus use (MI = "1") the device provides a second receive path the MIR pin and the RxMI output pin. The accompanying comparator thresholds are independent of the supply voltages and have a negligible delay time.

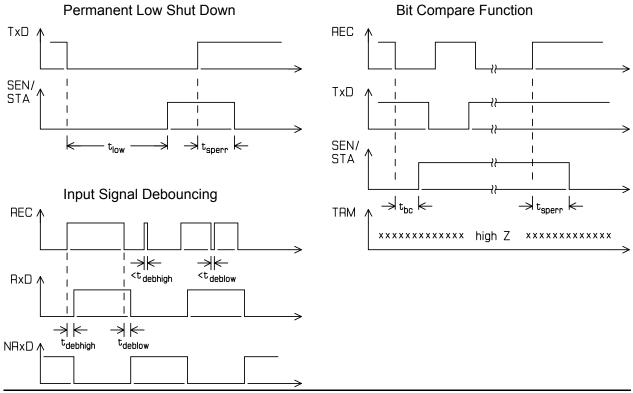

### 4.4. Bit-Compare-Function

If the TXD and REC signals differ by more than T<sub>bC</sub> the transmitter path is disabled. The transmit path is only made available again after TxD and REC are High for at least t<sub>sperr</sub> and no new disable signal is generated by the Bit-Compare-Function.

The Bit-Compare-Function is activated when the SEN/STA pin is open and the Pins MI and BCEN are at "0"

(See Table).

### 4.5. Permanent-low-Disconnection

The presence of a Low level on the TxD-Pin for time  $t_{IOW}$  (SEN/STA open, MI="0"),disables the transmitter path. A High-level on TxD for at least  $t_{recov}$  during the duration of  $t_{IOW}$  resets the permanent Low timer.

A disabled transmit path is only made available again when TxD and REC are High for longer than t<sub>sperr</sub> and no new disable is generated by the Bit-Compare-Function or the Permanent Low Disconnection.

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

PRODUCTION DATA - JUL 27, 2011

## E910.05

### 4.6. SEN/STA

The bi-directional pin SEN/STA flags the Transmitter status in KIP-Mode (MI = 0). The transmit path is disabled when SEN/STA = "1" and enabled when SEN/STA = "0". Since the driver capability of this pin is low (typically. 250µA) this can be overwritten by the microprocessor, ("Forced transmit status").

### 4.7. Functional Tables

#### 4.7.1. Pull-up-Resistor

| PU | MI | Pull-up             |

|----|----|---------------------|

| 0  | 0  | disabled            |

| 0  | 1  | to VCC (5V) MI-Mode |

| 1  | 0  | to VBAT (12V)       |

| 1  | 1  | to VBAT MI-Mode     |

#### 4.7.2. Bit Compare-Function

| BCEN | MI | Bit Compare |

|------|----|-------------|

| 0    | 0  | active      |

| 1    | 0  | inactive    |

#### 4.7.3. Status Transmitter

| SEN/STA | MI | Transmitter |

|---------|----|-------------|

| 0       | 0  | enabled     |

| 1       | 0  | disabled    |

| 0       | 1  | enabled     |

| 1       | 1  | enabled     |

## 4.9. Noise Immunity

The 910.05 device meets the following requirements of DIN 40 839 part 1, when used in an application according to this specification :

| Parameter       | Condition                                              |                                 |

|-----------------|--------------------------------------------------------|---------------------------------|

| Test pulse 1    | $t_1 = 5s / U_S = -100V$                               | 100 pulses                      |

| Test pulse 2    | t <sub>1</sub> = 0,5s / U <sub>S</sub> = 100V          | 1000 pulses                     |

| Test pulse 3a/b | DIN 40 839 Part 3<br>US = -150V / US = 100V            | 1000 Bursts                     |

| Test pulse 4    | $U_{s} = -6V U_{a} = -5V t_{8} = 5s$                   | 10 pulses                       |

| Test pulse 5    | $R_i = 2_t_D = 250ms$<br>$t_r = 0.1ms U_P + U_S = 40V$ | 10 pulses at 1 minute intervals |

PRODUCTION DATA - JUL 27, 2011

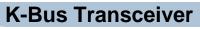

## 4.10. ESD Protection Circuit

#### 4.10.1. Test Method

The ESD Protection circuitry is measured using MIL-STD-883C Method 3015 (Human Body Model) with the following conditions :

VIN = 1000 Volt REXT = 1500 Ohm CEXT = 100 pF

PRODUCTION DATA - JUL 27, 2011

# E910.05

## 4.11. Operating Circuit

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

PRODUCTION DATA - JUL 27, 2011

#### WARNING – Life Support Applications Policy

ELMOS Semiconductor AG is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing ELMOS Semiconductor AG products, to observe standards of safety, and to avoid situations in which malfunction or failure of an ELMOS Semiconductor AG Product could cause loss of human life, body injury or damage to property. In development your designs, please ensure that ELMOS Semiconductor AG products are used within specified operating ranges as set forth in the most recent product specifications.

#### **General Disclaimer**

Information furnished by ELMOS Semiconductor AG is believed to be accurate and reliable. However, no responsibility is assumed by ELMOS Semiconductor AG for its use, nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of ELMOS Semiconductor AG. ELMOS Semiconductor AG reserves the right to make changes to this document or the products contained therein without prior notice, to improve performance, reliability, or manufacturability.

### **Application Disclaimer**

Circuit diagrams may contain components not manufactured by ELMOS Semiconductor AG, which are included as means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. The information in the application examples has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of ELMOS Semiconductor AG or others.

## **Contact Information**

#### Headquarters

| ELMOS Semiconductor AG<br>Heinrich-Hertz-Str. 1 • D-44227 Dortmund (Germany)                                                                                                          | © +492317549100 | ⊠: <u>sales@elmos.de</u><br> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|

| Regional Sales and Application Support Office Munich                                                                                                                                  |                 | T. <u>www.elmos.de</u>       |

| ELMOS Semiconductor AG<br>Am Geflügelhof 12 • 85716 Unterschleißheim/Eching                                                                                                           | © +49893183700  |                              |

| Sales Office France                                                                                                                                                                   |                 |                              |

| ELMOS FRANCE SAS<br>9/11 allée de l'Arche • La Défense • 92671 Courbevoie cedex (France)                                                                                              | © +33149971591  |                              |

| Sales and Application Support Office North America                                                                                                                                    |                 |                              |

| ELMOS NA. Inc.<br>32255 Northwestern Highway, Suite 45 • Farmington Hills, MI 48334                                                                                                   | © +12488653200  |                              |

| Sales and Application Support Office Korea and Japan                                                                                                                                  |                 |                              |

| ELMOS Korea<br>Dongbu Root building, 16-2, Suite 509, • Sunae-dong, Bundang-gu,<br>Seongnam-shi, Kyonggi-do (Korea)                                                                   | © +82317141131  |                              |

| Sales and Application Support Office China                                                                                                                                            |                 |                              |

| ELMOS Semiconductor Technology (Shanghai) Co., Ltd.<br>57-01E, Lampl Business Centre, 57F, The Exchange • 1486 Nanjing W Rd.<br>(299 Tongren Rd) • JingAn Shanghai • P.R.China 200040 | © +862161717358 |                              |

| Sales and Application Support Office Singapore                                                                                                                                        |                 |                              |

| ELMOS Semiconductor Singapore Pte Ltd.<br>60 Alexandra Terrace • #09-31 The Comtech • Singapore 118502                                                                                | © +6566351141   |                              |

© ELMOS Semiconductor AG, 2011. Reproduction, in part or whole, without the prior written consent of ELMOS Semiconductor AG, is prohibited.

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

ELMOS Semiconductor AG

Data Sheet 12/12