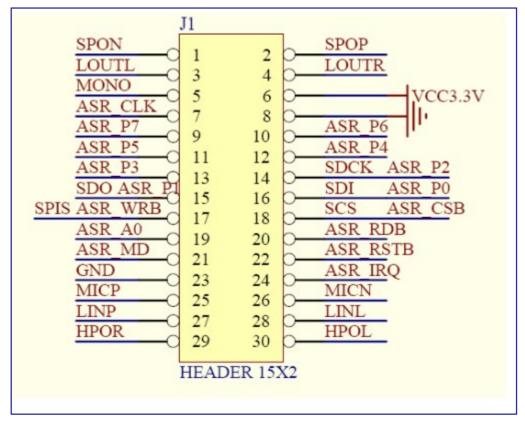

- The latest version, double rows pin, wiring and plug is very convenient!

- The board, by default external clock, users can also share active crystal rather than the external clock. Learning and application of the ideal module

- Schematics, 3 copies of STC C-language routines (play MP3, voice recognition and voice recognition and playback the MP3, with SPI and parallel two modes of operation of each program) and development board full set of information. (Direct online transfer)

- Before use, please see the module schematic and wiring instructions.

The LD3320 speech recognition module and the SYN6288 voice interaction module can be realized free recorded voice interaction. Two modules function complementary to the identification voice, but also for speech synthesis, as well as MP3, is to develop the ideal solution for next-generation voice control products.

ICRoute the launch LD332X non-specific speech recognition chip: 51MCU key words in Pinyin string set register incoming LD332X chip, you can complete voice recognition capabilities. Direct chip design system (LD332X chip support parallel port and SPI both interfaces the way) can increase the non-specific voice recognition functions.

#### The scenarios include:

- An electric stove / microwave / smart appliances operating

- navigators

- MP3/MP4

- Digital Photo Frame

- STB / TV remote control

- Intelligent toys / dialogue toys

- PMP / Game

- vending machine

- subway ticket vending machines

- · guides machine

- · buildings television advertising on demand

- public lighting systems / health systems / smart home, voice

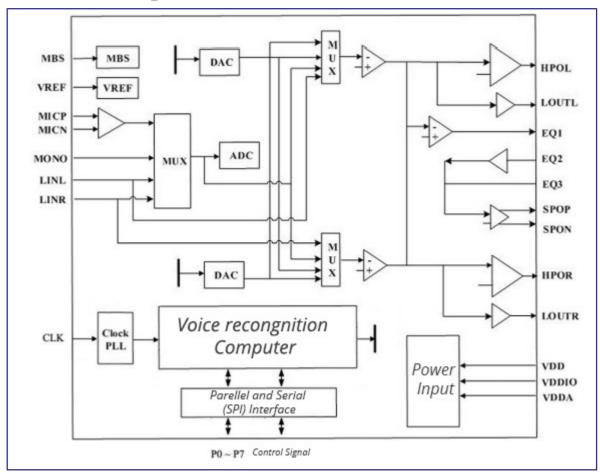

LD332X series ICRoute production based on non-specific speech recognition (SI-the ASR: Speaker-work of the Independent Automatic Speech Recognition) technology, voice recognition / voice chip. The series offers a true single-chip speech recognition solutions. The following LD3320 model to introduce the main features and characteristics of the chips, as well as voice recognition chip works as the representative.

LD332X family of chips designed to focus on energy conservation and efficiency, no external auxiliary chips such as Flash, RAM, the encryption chip and other integrated directly into existing products that can be achieved speech recognition / voice / man-machine dialogue function. And the identification of a list of key words can be dynamically edited.

Based on LD332X chip in any electronic products, and even including the most simple 51MCU as the system controller chips, easy voice recognition / voice / man-machine dialogue function. VUI (Voice User Interface) for all electronic products to increase the voice user interface. The user can combine the practical application scenarios to choose a different user usage patterns.

Verify that the voice recognition feature to help developers to quickly develop ICRoute to launch the voice recognition module M-LD3320, developers can easily integrate and develop the speech recognition feature.

#### LD332X series chips, the main features are:

• Fast and stable optimization algorithm to complete the speaker-independent voice recognition. Without your prior training and recording. Do not need any software on a PC.

- Single-chip.

- Do not need any external auxiliary Flash chips, RAM chips, and AD chip can complete voice recognition capabilities. Truly single-chip speech recognition solutions.

- Dynamic editing identification list.

- Each identify a maximum can be set to 50 candidates to identify the sentence, each identification sentence can be a word, phrase or phrases. On the other hand, identify the sentence content can be dynamically edit only need to master MCU to identify key words in the alphabet string by setting the register within the incoming chip. By a system supports a variety of scenes.

- The master MCU chip operation is completed through the read-write chip internal registers. Through the settings and read the register can be easily set up a list of speech recognition, start voice recognition, access to the recognition result, play MP3 and other functions.

- The chip has been prepared within the 16-bit A / D converter, 16-bit D / A converter and amplifier circuit. Microphone, stereo headphone and mono speaker can be easily connected to chip pin. Stereo headphone jack output power of 20mW, the output power of the speaker interface 550mW loud and clear sound.

- Support a parallel interface and serial interface SPI two connections, serial way to simplify the connection with other modules.

- The chip is set to hibernation, then the power consumption is very small, and can be easily activated.

- Support for MP3 playback, without the need for external auxiliary devices, the master MCU to MP3 data followed into chip LD332X within the sound output from chip D / A PIN.

Support MPEG1 (ISO/IEC11172-3), MPEG2 (ISO/IEC13818-3) and MPEG 2.5 layer 3 and other formats.

- Work power supply is 3.3V, if used in portable systems, uses 3 AA batteries to meet power supply needs.

LD3320 is a "special chip that integrates a speech recognition processor with some external circuits, including AD, DA converters, microphone interface, audio output interface. This chip does not

require any external auxiliary chip Flash, RAM, etc., directly integrated in existing products that can do speech recognition / voice / man-machine dialogue function. Further, the identification of a list of key words is any dynamic edited.

## Main features are

- Via ICRoute unique fast and stable optimization algorithm, complete the non-specific human speech recognition. Does not require prior training and recording, recognition accuracy rate of 95%.

- Do not need any external auxiliary Flash chip, RAM chips and AD chip, you can complete a language voice recognition function. Truly provides a single-chip speech recognition solutions.

- Each identification may be provided up to 50 candidate recognition sentences, each identification sentence can be a word, phrase, or phrases, the Pinyin string of a length of not more than 10 characters, or 79 bytes. Other hand, discrimination sentence content can be dynamically editorial changes by a system supports a variety of scenes.

- The chip has been prepared within the 16-bit A / D converter, 16-bit D / A converter and amplifier circuit, a microphone, stereo headphones and a mono speaker can be easily connected to the chip pin. Stereo headphone jack of the output power is 20mW, and the speaker interface output power of 550mW, and can produce a clear and loud voice.

- Supports parallel and serial interface, Serial ways to simplify the connection with other modules.

- Can be set to the sleep state, and can be easily activated.

- Supports MP3 playback, without external auxiliary device, the master MCU MP3 data then sent to the LD3320 chip inside can the corresponding PIN output sound from the chip.Product design can choose to get the sound output from the stereo headphones or mono speaker.Support MPEG1 (ISO/IEC11172-3), MPEG2 (ISO/IEC13818-3) and MPEG 2.5 layer 3 and other formats.

- The working power supply of 3.3V, use three AA batteries to meet the power supply needs for portable systems.

# **Circuit Description**

Described in detail as follows:

# Voltage requirements

VDD - digital circuit power input - 3.0 V - 3.3 V

VDDIO - digital I / O circuit power input - 1.65 V - VDD

VDDA - analog circuit power input - 3.0 V - 4.0 V

Recommended that the user can use the unified 3.3v voltage input to simplify the design. Digital voltage and analog voltage into Line isolation can make the chip has a better effect.

Chip pin input voltage range:

A high voltage (logic "1")))): 0.7 \* VDDIO ~ VDDIO

A low voltage (logic "0"): 0 ~~ 0.3 \* VDDIO

Therefore, developers need to ensure their own master MCU using the same kind of work in 3.3v, master MCU to the LD3320 pin output high voltage does not exceed 3.3V.

# Clock (Clock)

The chip must be connected to an external clock, 4-48MHz frequency range is acceptable; while the chip also A PLL frequency synthesizer, a specific frequency can be generated for use by the internal module.

### Reset

The chips reset signal (RSTB \*) VDD / VDDA / VDDIO stable. No matter what chip ongoing operation, the reset signal can be made to restore the initial state, and each register is reset. If you do

not follow the instructions (register settings) after reset chip into hibernation. Since then, a CSB \* signal can reactivate the chip to enter the work state.

#### **Parallel Interface**

The chip can be connected in parallel and an external host CPU, this time using the eight data lines (P0-P7)and four control signals (WRB \*, RDB \*, CS \*, A0), and an interrupt return signal (INTB \*).

#### **Serial Interface**

The serial interface is connected via the SPI protocol and external host CPU, First set MD to high, and (SPIS \*) ground. Use only four pins: chip select (SCS \*), the the SPI clocks (SDCK) SPI input (SDI) and SPI output (SDO).

## Register

Settings and commands on the chip, including the transmit data and receive data, through the operation of the register to complete. For example, voice recognition, set identified a list of key words, setting the recognition mode of the chip, after the recognition is complete guide to the recognition result is accomplished through read / write registers. Play a sound, the MP3 format is the data cycle into the FIFO corresponding to the register. (Recognition result is returned through the register to identify key words arranged in a list of key words serial Index value, the Index value is specified in setting up a list of key words)

## The external control of the speaker volume

In addition to specific registers to control the volume, the the chip external circuit can control the speaker volume gain. EP1, EP2, EP3 corresponding pin. See Appendix B

# **Pins Definitions**

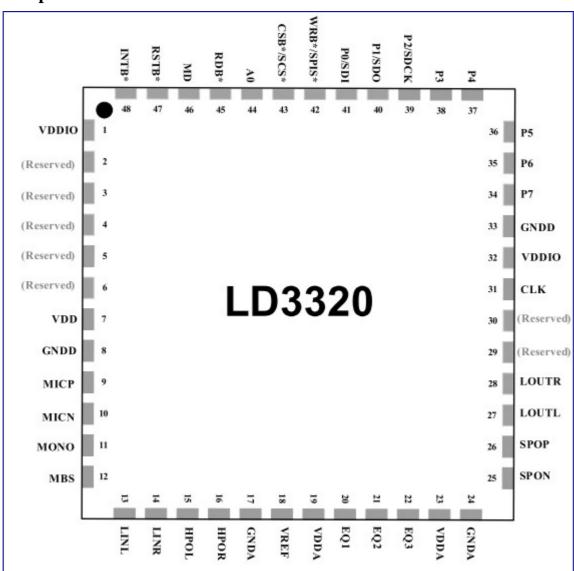

| Number | Name        | IO<br>Direction | AD<br>type | Descripition                                                    |

|--------|-------------|-----------------|------------|-----------------------------------------------------------------|

| 1, 32  | VDDIO       | -               | -          | Digital I / O circuit power input                               |

| 2      | (Reaserved) | -               | -          | (Pull-up resistor connected according to the circuit schematic) |

| 3      | (Reaserved) | -               | -          | (Pull-up resistor connected according to the circuit schematic) |

| 4      | (Reaserved) | -               | -          | (Pull-up resistor connected according to the circuit schematic) |

| 5      | (Reaserved) | -               | -          | (Pull-up resistor connected according to the circuit schematic) |

| 6      | (Reaserved) | -               | -          | Can be null                                                     |

| 7      | VDD         | -               | D          | Power or VCC for digital circuit                                |

| 8, 33  | GNDD        | -               | D          | Ground for IO and digital circuits                              |

| 9, 10  | MIC[P, N]   | I               | A          | Microphone input (positive and negative terminals)              |

| 11     | MONO        | I               | A          | Mono lineIn input                                               |

| 12     | MBS         | -               | A          | Microphone bias                                                 |

| 13, 14 | LIN[L, R]   | I               | A          | Stereo LineIn (left and right ends)                             |

| Number | Name        | IO<br>Direction | AD<br>type | Descripition                                                                                                                              |

|--------|-------------|-----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 15, 16 | HPO[L, R]   | O               | A          | Headphone output (left and right side)                                                                                                    |

| 17     | GNDA        | -               | A          | Ground for analog circuit                                                                                                                 |

| 18     | VREF        | -               | A          | Sound signal reference voltage                                                                                                            |

| 19, 23 | VDDA        | -               | A          | VCC for analog circuit                                                                                                                    |

| 20     | EQ1         | O               | A          | Speaker volume external control 1                                                                                                         |

| 21     | EQ2         | I               | A          | Speaker volume external control 2                                                                                                         |

| 22     | EQ3         | O               | A          | Speaker volume external control 3                                                                                                         |

| 24     | GNDA        | -               | A          | Ground for analog circuit                                                                                                                 |

| 25, 26 | SPO[N, P]   | O               | A          | Speaker Output                                                                                                                            |

| 27, 28 | LOUT[L, R]  | O               | A          | LineOut Output                                                                                                                            |

| 29     | (Reaserved) | -               | -          | (Refer to Appendix B.4 instructions)                                                                                                      |

| 30     | (Reaserved) | -               | -          | (Refer to Appendix B.4 instructions)                                                                                                      |

| 31     | CLK         | I               | D          | Clock input 2-34 (MHz)                                                                                                                    |

| 34     | P7          | I/O             | D          | (7) parallel port connection on the pull-up resistor                                                                                      |

| 35     | P6          | I/O             | D          | (6) parallel port connection on the pull-up resistor                                                                                      |

| 36     | P5          | I/O             | D          | (5) parallel port connection on the pull-up resistor                                                                                      |

| 37     | P4          | I/O             | D          | (4) parallel port connection on the pull-up resistor                                                                                      |

| 38     | P3          | I/O             | D          | (3) parallel port connection on the pull-up resistor                                                                                      |

| 39     | P2/SDCK     | I/O             | D          | (2) Parallel port, shared SPI clock, connect the pull-up resistor                                                                         |

| 40     | P1/SDO      | I/O             | D          | (1) parallel port, shared SPI output                                                                                                      |

| 41     | P0/SDI      | I/O             | D          | Parallel port (0), shared the SPI input, connect the pull-<br>up resistor                                                                 |

| 42     | WRB*/SPIS * | I               | D          | Write enable (active low), shared SPI allowing (active low), connect the pull-up resistor                                                 |

| 43     | CSB*/SCS*   | I               | D          | Parallel chip select signals, the shared SPI chip select signals connected to the pull-up resistor                                        |

| 44     | A0          | I               | D          | Address or data selection.WRB * effective, high indicates P0 $\sim$ P7 is the address, while the low P0 $\sim$ P7 data. Pull-up resistors |

| 45     | RDB*        | I               | D          | Reading allows (active low), connect the pull-up resistor                                                                                 |

| 46     | MD          | I               | D          | 0: parallel work, 1: serial work (SPI protocol), connect the pull-up resistor                                                             |

| 47     | RSTB*       | I               | D          | Reset signal (active low), connect the pull-up resistor                                                                                   |

| 48     | INTB*       | O               | D          | Interrupt output signal (active low), Connect with Pull-up resistors                                                                      |

Description: IO represents direction: I represents input; O represents the output. AD represents: A represents the analog signal; D represents the digital signal.

# The pin distribution as shown below:

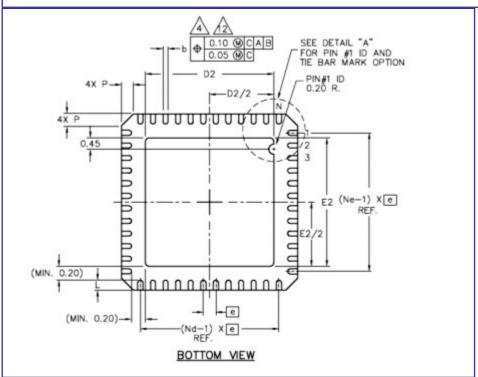

# Appendix A

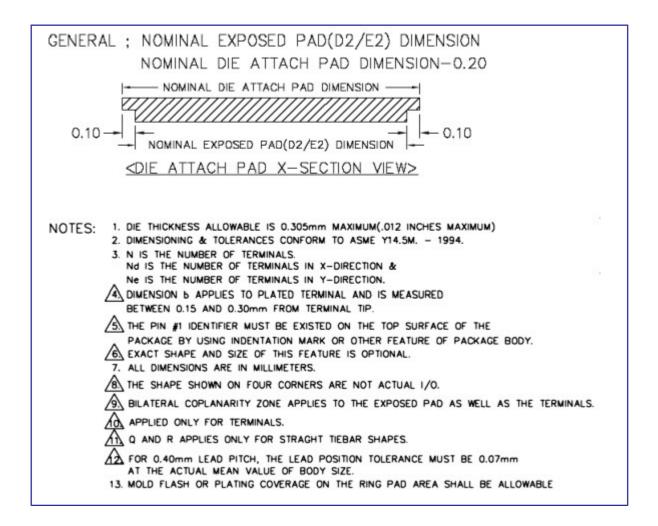

The chip uses a 48-pin QFN plastic package, the size of about 7 \* 7 \* .85 mm, compact, and pin arrangement is reasonable. Below is the actual image of the front of the package.

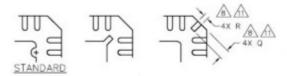

FOR ODD TERMINAL/SIDE FOR EVEN TERMINAL/SIDE

DETAIL "A" - PIN #1 ID AND TIEBAR MARK FIGURES

| S                     |      | COMMON     | 1    |      |  |  |  |

|-----------------------|------|------------|------|------|--|--|--|

| B                     | DI   | DIMENSIONS |      |      |  |  |  |

| S<br>W<br>B<br>O<br>L | MIN. | NOM.       | MAX. | No,  |  |  |  |

| Α                     | 0.80 | 0.85       | 0.90 |      |  |  |  |

| A1                    | 0.00 | 0.01       | 0.05 | 10   |  |  |  |

| A2                    | 0.60 | 0.65       | 0.70 |      |  |  |  |

| A3                    |      | 0.20 REF.  |      | 3    |  |  |  |

| D                     |      | 7.00 BSC   |      |      |  |  |  |

| D1                    |      | 6.75 BSC   |      |      |  |  |  |

| E                     |      | 7.00 BSC   |      |      |  |  |  |

| E1                    |      | 6.75 BSC   |      |      |  |  |  |

| θ                     | 0    | _          | 12*  |      |  |  |  |

| Р                     | 0.24 | 0.42       | 0.60 |      |  |  |  |

| Q                     | 0.30 | 0.40       | 0.65 | 8,11 |  |  |  |

| R                     | 0.13 | 0.17       | 0.23 | 8,11 |  |  |  |

| S . W B O | PITCH VARIATION           |          |      |     |  |

|-----------|---------------------------|----------|------|-----|--|

| ီု        | MIN.                      | NOM.     | MAX. | °τε |  |

| e         |                           | 0.50 BSC |      |     |  |

| N         |                           | 48       |      | 3   |  |

| Nd        | 12                        |          |      |     |  |

| Ne        | V-Value representation of | 12       |      | 3   |  |

| L         | 0.30                      | 0.40     | 0.50 |     |  |

| b         | 0.18                      | 0.23     | 0.30 | 4   |  |

| D2        | 5.40                      | 5.50     | 5.65 |     |  |

| E2        | 5.40                      | 5.50     | 5.65 | -   |  |

# **Appendix B: Auxiliary circuit**

## The external control of the speaker volume

The external circuit can change the volume of the speaker, for example, the resistor R6 and the resistance R2 in the following diagram for the 33K and 15K, respectively, then the 33/15 = 2.2, the sound is amplified by about 2 times. If given the variable resistor R6 access, you can manually adjust the volume. Recommends that users adopt a structure similar to the one in Figure B-1 circuit.

## The microphone bias of auxiliary circuit

Pin 12 (MBS) is the microphone bias, to pick up an RC circuit can output a floating voltage to the microphone. Recommends that users adopt a structure similar to the one in Figure B-2 circuit.

# Correct soldering Pull-up resistors ensure the stable system work

"LD3320 test board schematic gives recommendations on the pull-up resistor,  $P0 \sim P7$ , MD, RDB, CSB, INTB, WRB, RSTB, A0 control pins connected to the 1k/10k upper pull-up resistor, it is recommended that the design try welding pull-up resistor to ensure that the chip control port signal stability, the stability of the auxiliary systems.

# Chip analog signal pin needs to correct welding auxiliary circuit

"LD3320 test board schematic gives the periphery of the auxiliary circuits of the chip analog signal pin, including Audio the Input; Audio Output; EQ1/EQ2/EQ3 external speaker volume control

circuit; analog power auxiliary circuit. Designers must given according to the schematic diagram of the "LD3320 Beta capacitance / resistance device is properly soldered these auxiliary circuit, in order to ensure that the chip's analog module can work normally.

# Chip pin 29, the pin 30 of the instructions

Chip pin 29 and the pin 30, the chip restart after reset (RSTB \*), a low output voltage stability. Developers can connect the two pin LED, as shown in the chip power-on indication (such as "LD3320 test board schematic connection). Directly to the two pin vacant.